HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.

₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

Source : Verilog HDL

Base Paper Abstract:

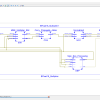

Approximate computing is an emerging paradigm in error-tolerant applications that leads to power-efficient designs without significant loss in quality. The divider in these applications have complex hardware and more latency among the computational blocks resulting in power consumption. Hence approximating the division module would lead to designs with vastly improved power efficiency. A new approximate subtractor (AxSUB) is proposed in this paper with the intent to reduce the hardware complexity while achieving accuracy within permissible limits. The proposed AxSUB and existing approximate subtractor units are used in the restoring array division (RAD) architecture to prove the efficacy of the AxSUB. Comprehensive error and synthesis analysis are performed on RAD architectures implemented using AxSUB, and existing methods. Our proposed design achieved a 21% decrease in area and a 28% decrease in power consumption compared to the exact design. The proposed and existing RAD architectures is implemented on change detection applications to validate the quality-effort tradeoff.

List of the following materials will be included with the Downloaded Backup:

Proposed Title :

Improvement of this project :

Software Implementation:

Proposed System:

It is possible to apply approximation computing in error-tolerant applications in order to decrease the amount of power that is used while simultaneously increasing the level of overall circuit performance. The three approximation divisions that are shown in this study all employ an array-based architecture. As a result, they are able to accomplish considerable hardware savings while maintaining a high degree of accuracy in comparison to other contemporary approximate designs. An emerging paradigm in error-tolerant applications, approximate computing results in designs that use less power while maintaining a comparable level of quality to their more traditional counterparts. The divider in these applications has complicated circuitry, which results in higher delay between the various computing blocks and increases the amount of power consumption. Therefore, coming up with an approximation for the division module would result in designs that were far more power efficient. In this research, we propose a novel algorithm called approximate subtraction (AxSUB) with the goal of reducing the complexity of the hardware while still obtaining accuracy within the allowable bounds of the algorithm. In order to demonstrate the usefulness of the AxSUB, both the proposed AxSUB and the current approximate subtraction units are included into the restoring array division (RAD) architecture. The effectiveness of the proposed designs for the AxSUB (8/4) and the AxSUB (16/8) was shown. The XRMDC (8/4) design, which was suggested, improved the accuracy of the column-wise function, but the XRMDC (16/8) design uses a number of rows with correct architectural function. An extensive accuracy and performance test is carried out on the recommended dividers, along with a number of additional designs that are regarded as representing the state of the art. In contrast to a design that is accurate, the divisions that have been proposed have a more compact form factor, a reduced need for power, and a higher degree of accuracy, all while contributing just a marginal amount of error. In addition, the trade-off between accuracy and higher performance for various approximation divisions is explored in order to determine which designs achieve the best compromise. This is done in order to find which designs provide the best possible outcome. This is done in order to determine which designs strike the optimal balance between the two competing elements. This proposed architecture was created using Verilog HDL, synthesized with Xilinx Vertex-5 FPGA, and all of the parameters were studied and compared with respect to area, latency, and power.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

HDFC BANK ACCOUNT:

₹35,000.00 Original price was: ₹35,000.00.₹20,000.00Current price is: ₹20,000.00.

₹16,000.00 Original price was: ₹16,000.00.₹10,000.00Current price is: ₹10,000.00.

Copyright © 2026 Nxfee Innovation.