HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.

₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

Source : Verilog HDL

Base Paper Abstract:

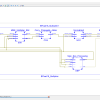

Addition units are widely used in many computational kernels of several error-tolerant applications such as machine learning and signal, image, and video processing. Besides their use as stand-alone, additions are essential building blocks for other math operations such as subtraction, comparison, multiplication, squaring, and division. The parallel prefix adders (PPAs) is among the fastest adders. It represents a parallel prefix graph consisting of the carry operator nodes, called prefix operators (POs). The PPAs, in particular, are among the fastest adders because they optimize the parallelization of the carry generation (G) and propagation (P). In this work, we introduce approximate PPAs (AxPPAs) by exploiting approximations in the POs. To evaluate our proposal for approximate POs (AxPOs), we generate the following AxPPAs, consisting of a set of four PPAs: approximate Brent–Kung (AxPPA-BK), approximate Kogge–Stone (AxPPAKS), Ladner-Fischer (AxPPA-LF), and Sklansky (AxPPA-SK). We compare four AxPPA architectures with energy-efficient approximate adders (AxAs) [i.e., Copy, error-tolerant adder I (ETAI), lower-part OR adder (LOA), and Truncation (trunc)]. We tested them generically in stand-alone cases and embedded them in two important signal processing application kernels: a sum of squared differences (SSDs) video accelerator and a finite impulse response (FIR) filter kernel. The AxPPA-LF provides a new Pareto front in both energy-quality and area-quality results compared to state-of-the-art energy-efficient AxAs.

List of the following materials will be included with the Downloaded Backup:

Proposed System:

The computational kernels of many error-tolerant applications, including machine learning and signal, image, and video processing, extensively make use of addition units. In addition to their utility as independent operations, additions are crucial building blocks for a variety of other mathematical operations, including subtraction, comparison, multiplication, squaring, and division. The parallel prefix adders (PPAs), which are also known as PPAs, are among the most efficient adders. It is an illustration of a parallel prefix structure that is made up of carry operator nodes that are referred to as prefix operators (POs). PPAs in particular are some of the most efficient adders due to the fact that they optimize the parallelization of carry generation (G) and propagation (P), making them among the quickest adders. We take use of approximations in the POs to develop approximate PPAs (AxPPAs), which we present in this study. In addition, instead of a two-operand adder, a three-operand adder may be used, which results in a significant reduction in the critical path latency. However, this comes at the price of more hardware. In many different cryptography and pseudorandom bit generator (PRBG) techniques, the three-operand binary adder is the fundamental functional unit that is used to conduct the modular arithmetic. In order to test our proposal for approximate POs (AxPOs), we have generated the following AxPPAs, which are comprised of a set of five PPAs: approximate Brent–Kung (AxPPA-BK), approximate Kogge–Stone (AxPPA-KS), Ladner–Fischer (AxPPA-LF), Sklansky (AxPPA-SK), and Han–Carlson (AxPPA-HCA). We evaluate the performance of five different AxPPA designs by comparing them with energy-efficient approximation adders (AxAs) and the Proposed Three Operand Adder. This includes proving the performance in terms of area, latency, and power.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

HDFC BANK ACCOUNT:

₹16,000.00 Original price was: ₹16,000.00.₹10,000.00Current price is: ₹10,000.00.

₹25,000.00 Original price was: ₹25,000.00.₹15,000.00Current price is: ₹15,000.00.

Copyright © 2026 Nxfee Innovation.