₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

Source : Verilog HDL

Abstract:

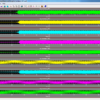

As a traditional digital platform, Field Programmable Gate Array (FPGA) is seldom used for analog applications. Since there is no way to fine tune the gate property or circuit structure, the performance of FPGA analog application is usually inferior to its counterparts based on full-custom or even cell-based design. Nevertheless, a high performance FPGA time-to-digital Converter (TDC) is proposed in this paper to expand the FPGA territory into high-end analog applications. The test time signal is sampled by a serious timing references generated by feeding the original clock into a tapped delay line. According to periodicity, the delays among those timing references are wrapped into a single reference period and the effective TDC resolution can be made much smaller than the clock period to compete even with the state-of the art full-custom TDCs in performance. After measurement, the effective resolution is as fine as 2.5 ps. The corresponding differential nonlinearity (DNL) is -1.90~1.66 LSB and the integral nonlinearity (INL) is -3.79~6.53 LSB only.

List of the following materials will be included with the Downloaded Backup:

Proposed Title :

Improvement of this project :

Software implementation:

Proposed System:

Time to Digital Converter provides the digital representation of time when it occurs. The major requirements for main stream applications include wide measurement range, high resolution, low cost and low process, voltage and temperature (PVT) sensitivity. To achieve resolutions better than 10 ps, most TDCs are implemented in application-specific integrated circuits (ASIC), which is ineffective. Therefore, This paper proposes the new concept of Time-to-digital Converter(TDC) FPGA with high resolution of 2ps(picoseconds) bin size. This concept increases the performance of TDC in order to achieve a high resolution. In this concept the signals are sampled with n number of times and timing reference is generated by feeding original clock into tapped delay line. According to periodicity, the delays among those timing references are wrapped into a single reference period and the effective TDC resolution can be made much smaller than the clock period to compete even with the state-of the art full-custom TDCs in performance. Finally, this concept of High resolution of TDC is implemented in the VERILOG and Synthesized using XILINX and shown the comparison in terms of delay, power and area reports.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

₹12,000.00 Original price was: ₹12,000.00.₹8,000.00Current price is: ₹8,000.00.

₹12,000.00 Original price was: ₹12,000.00.₹8,000.00Current price is: ₹8,000.00.

Copyright © 2026 Nxfee Innovation.

Reviews

There are no reviews yet.