₹35,000.00 Original price was: ₹35,000.00.₹12,000.00Current price is: ₹12,000.00.

Source : VHDL / Verilog HDL

Abstract:

In this paper, a double-error-correcting and triple error-detecting (DEC-TED) Bose–Chaudhuri–Hocquenghem (BCH) code decoder with high decoding efficiency and low power for error correction in emerging memories is presented. To increase the decoding efficiency, we propose an adaptive error correction technique for the DEC-TED BCH code that detects the number of errors in a codeword immediately after syndrome generation and applies a different error correction algorithm depending on the error conditions. With the adaptive error correction technique, the average decoding latency and power consumption are significantly reduced owing to the increased decoding efficiency. To further reduce the power consumption, an invalid-transition-inhibition technique is proposed to remove the invalid transitions caused by glitches of syndrome vectors in the error-finding block. Synthesis results with an industry-compatible 65-nm technology library show that the proposed decoders for the (79, 64, 6) BCH code take only 37%–48% average decoding latency and achieve more than 70% power reduction compared to the conventional fully parallel decoder under the 10−4–10−2 raw bit-error rate.

List of the following materials will be included with the Downloaded Backup:

Proposed Title :

Improvement of this Project:

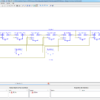

Software implementation:

Proposed System:

The Spin-transfer torque magneto resistive random access memory(SST_MRAM) Emerging memories are considered to be the promising candidate embedded memories due to their fast and write latencies, low leakage power, and logic-friendly compatibility. As technology scales down, these emerging memories are also struggling with reduced reliability, and as a solution, error-correcting code and its encoder and decoder circuits have been applied. Therefore, this paper proposes the efficient Double Error Corrector and Triple Error Detector (DEC-TED) Bose-Chaudhuri-Hocquenghem (BCH) decoder with high efficiency and low power for emerging memories are presented. The proposed efficient double error corrector and triple error detector includes the blocks of syndrome generator, error counter, single error corrector, double error corrector and error correction. The adaptive error correction technique is proposed for double error corrector and triple error detector BCH code to detect the number of error in the codeword immediately after the syndrome generation and checks the error of the code word based on the error which depends upon the different error correction algorithm which are used in the proposed decoding technique. This adaptive error correcting technique reduces the power consumption and increases the decoding efficiency compared to existing decoding technique. The invalid transition inhibition technique is implemented to remove the invalid transition caused by the glitches of the syndrome vectors in the error finding block. Thus, reduces the further more power consumption in the decoding technique. Finally, theses technique is implemented in the VHDL and synthesized in the XILINX FPGA-S6LX9 and shown the comparison in terms of area, power and delay reports.

PROPOSED HIGH-DECODING-EFFICIENCY AND LOW-POWER DEC-TED BCH DECODER

In this section, a DEC-TED BCH decoder using an adaptive error correction and an invalid transition inhibition technique is proposed to achieve the high decoding efficiency and low-power consumption.

As an example, let us consider a simple BCH code. In this case, the three parity check bits p0, p1, p2, p3, p4, p5, p6, p7, p8, p9, p10 are computed as a function of the data bits d1, d2, d3, d4, d5, d6, d7, d8, d9, d10, d11, d12 as follows:

P0 = d1 + d2 + d3 + d4 + d5 + d6 + d7 + d8 + d9 + d10 + d11

P1 = d1 + d2 + d3 + d4 + d5 + d6 + d7 + d8 + d9 + d10 + d12

P2 = d1 + d2 + d3 + d4 + d5 + d6 + d7 + d8 + d9 + d11 + d12

P3 = d1 + d2 + d3 + d4 + d5 + d6 + d7 + d8 + d10 + d11 + d12

P4 = d1 + d2 + d3 + d4 + d5 + d6 + d7 + d9 + d10 + d11 + d12

P5 = d1 + d2 + d3 + d4 + d5 + d6 + d8 + d9 + d10 + d11 + d12

P6 = d1 + d2 + d3 + d4 + d5 + d7 + d8 + d9 + d10 + d11 + d12

P7 = d1 + d2 + d3 + d4 + d6 + d7 + d8 + d9 + d10 + d11 + d12

P8 = d1 + d2 + d3 + d5 + d6 + d7 + d8 + d9 + d10 + d11 + d12

P9 = d1 + d2 + d4 + d5 + d6 + d7 + d8 + d9 + d10 + d11 + d12

P10 = d1 + d3 + d4 + d5 + d6 + d7 + d8 + d9 + d10 + d11 + d12

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

₹10,000.00 Original price was: ₹10,000.00.₹6,000.00Current price is: ₹6,000.00.

Copyright © 2026 Nxfee Innovation.