Proposed Title:

FPGA Implementation of Area Efficient Dual Quality Approximate Convolution Systolic Array Architecture

Improvement of this project :

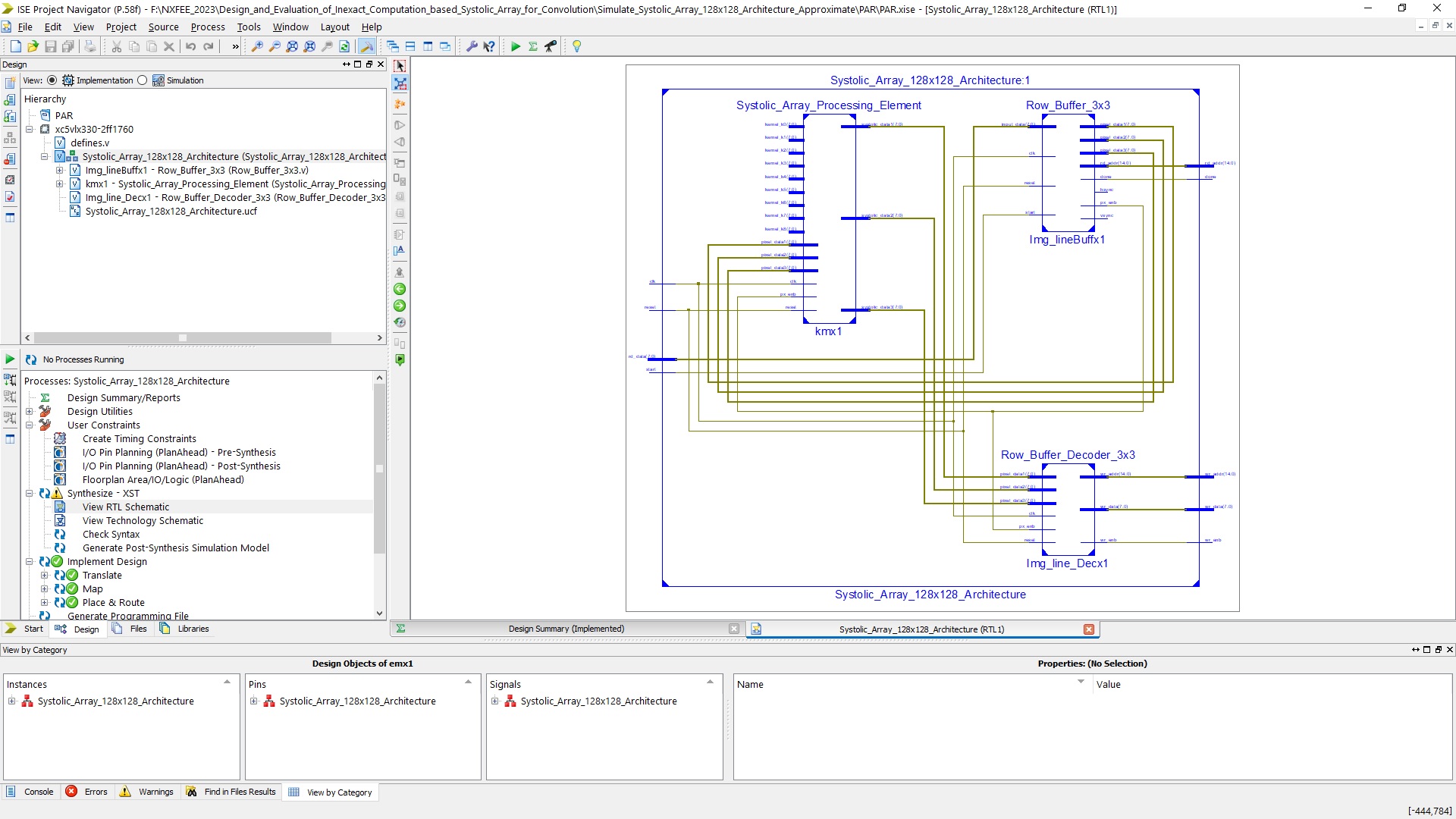

To design a Systolic Array based 128×128 Convolution Operation using 3×3 kernel size (convolution Filter)

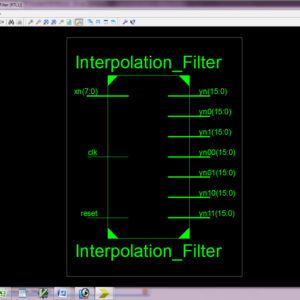

To design 8×8 Dual quality approximate multiplier and integrate into convolution method, and compared with exact multiplier based convolution method.

Design done with Verilog HDL, and synthesized using Xilinx Vertex-5 FPGA and compared all the parameters in terms of area, delay and power.

Software Implementation:

- Modelsim

- Xilinx

Proposed System:

This study introduces an FPGA implementation of a systolic array-based 128×128 convolution operation, leveraging a novel 8×8 dual quality approximate multiplier designed for image processing applications. The systolic array, configured with a 3×3 convolution kernel, utilizes the parallel processing capabilities of FPGAs to achieve high-throughput computation. The proposed 8×8 dual quality approximate multiplier provides a flexible approach to balancing computational accuracy and hardware efficiency. The complete design is described in Verilog HDL and synthesized using the Xilinx Virtex-5 FPGA platform. A comprehensive evaluation comparing the approximate multiplier-based convolution method with the traditional exact multiplier-based method is conducted, focusing on key performance metrics such as area, delay, and power consumption. Our results demonstrate that the dual quality approximate multiplier significantly reduces hardware resource utilization and power consumption. This work contributes to the development of efficient, compact, and adaptive hardware architectures for modern convolutional neural network (CNN) implementations.

” Thanks for Visit this project Pages – Buy It Soon “

Design and Evaluation of Inexact Computation based Systolic Array for Convolution

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.