HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.

₹14,000.00 Original price was: ₹14,000.00.₹10,000.00Current price is: ₹10,000.00.

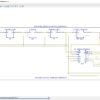

Source : Verilog HDL

Base Paper Abstract:

Approximate computing is an emerging paradigm for trading off computing accuracy to reduce energy consumption and design complexity in a variety of applications, for which exact computation is not a critical requirement. Different from conventional designs using AND-OR and XOR gates, the majority gate is widely used in many emerging nanotechnologies. An ultra-efficient 6-2 compressor is proposed in this paper. It is composed of two majority gates that lead to low energy consumption and high hardware efficiency. The proposed compressor is utilized in the approximate partial product reduction of a modified 8×8 Dadda multiplier with a truncated structure. Experimental results show that this multiplier realizes a significant reduction in hardware cost, especially in terms of power and area, on average by up to 40% and 31% respectively, compared to exact and state-of-the-art designs. The application of image multiplication is also presented to assess the practicability of the multiplier. The results show that the proposed multiplier results in images with higher quality in peak signal to noise ratio (PSNR) and mean structural similarity index metric (MSSIM) compared to other designs.

List of the following materials will be included with the Downloaded Backup:

Proposed System:

In this work, we propose a novel approach to design a hardware-efficient 2D convolution operation using a 4×4 matrix and a 2×2 kernel multiplication with Majority Logic Compressor (MLC) based Approximate Multiplier. The convolution operation plays a pivotal role in various signal processing and image processing applications, including feature extraction, filtering, and pattern recognition. However, conventional convolution implementations often require significant hardware resources, especially for high-resolution inputs. To address this challenge, we leverage the MLC-based Approximate Multiplier, which offers a trade-off between accuracy and hardware complexity. Our design integrates the MLC-based multiplier into the convolution operation, replacing conventional multipliers to reduce hardware overhead while maintaining reasonable accuracy. We describe the design process, including the specification of the input matrix and kernel, the implementation of the convolution operation, and the design of the MLC-based Approximate Multiplier using Verilog HDL. Furthermore, we discuss testing, evaluation, and optimization strategies to validate the functionality and performance of the proposed design which using Xilinx Spartan-6 FPGA. Our results demonstrate the effectiveness of the proposed approach in achieving hardware-efficient 2D convolution with reduced resource utilization and acceptable accuracy for various applications.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

HDFC BANK ACCOUNT:

₹25,000.00 Original price was: ₹25,000.00.₹15,000.00Current price is: ₹15,000.00.

₹20,000.00 Original price was: ₹20,000.00.₹16,000.00Current price is: ₹16,000.00.

Copyright © 2026 Nxfee Innovation.