HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.

₹25,000.00 Original price was: ₹25,000.00.₹16,000.00Current price is: ₹16,000.00.

Source : Verilog HDL

Base Paper Abstract:

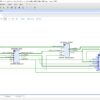

2-Dimensional fast Fourier transform (FFT) has been widely used in radar signal process. Due to the need for high performance, field programmable gate array (FPGA) is an ideal hardware device for this application. For space-borne radar platform such as synthetic aperture radar (SAR), single-event upsets (SEUs) can cause lots of soft errors in static random access memory (SRAM) based FPGA. As to this, protecting the 2D-FFT implemented in FPGA from SEUs is very important. In this article, we analyze the critical weakness induced by SEUs in the 2D-FFT process, and then a 2D-FFT design with high SEU resilience is presented. The design utilizes the advantage of several anti-SEU methods. For butterfly control in FFT, partially triple modular redundancy (TMR) is used. For data buffers, error correction code (ECC) is applied to read and write operation. Furthermore, safe finite state machine (FSM) is adopted by important control registers. Fault injection results show that all these reinforcement technologies contribute to enhance the ability to mitigate the SEU effects.

List of the following materials will be included with the Downloaded Backup:

Proposed System:

The two-dimensional fast Fourier transform (FFT) has been widely employed in the processing of radar signals. Field programmable gate array (FPGA) is an excellent hardware solution for this application due to the necessity for high performance. Single-event upsets (SEUs) in static random access memory (SRAM)-based FPGAs can produce a large number of soft errors in space-borne radar platforms such as synthetic aperture radar (SAR). In this regard, safeguarding the 2D-FFT implemented in FPGA against SEUs is critical. In this paper, we examine the significant weakness caused by SEUs in the 2D-FFT process and then provide a 2D-FFT design with strong SEU resilience. The design takes advantage of many anti-SEU techniques. Partially triple modular redundancy (TMR) is utilized in FFT for butterfly control. When reading and writing data buffers, error correcting code (ECC) is used. Furthermore, critical control registers use secure finite state machines (FSM). The findings of fault injection reveal that all of these reinforcement approaches help to improve the capacity to attenuate SEU impacts. Instead of radix-2, the proposed architecture builds the SEU Tolerant 2D-FFT utilizing radix-4 design architecture to minimize the number of iterations in 2D-FFT. To minimize the logic size with garbage signals, SEU Tolerant 2D-FFT was designed utilizing Reversible Array Multiplier. The proposed structure was compared to the conventional Array multiplier and the performance of area, latency, and power in the Xilinx Vivado Aritix-7 FPGA was demonstrated.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

HDFC BANK ACCOUNT:

₹18,000.00 Original price was: ₹18,000.00.₹10,000.00Current price is: ₹10,000.00.

₹12,000.00 Original price was: ₹12,000.00.₹6,000.00Current price is: ₹6,000.00.

Copyright © 2026 Nxfee Innovation.