HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.

₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

Source : Verilog HDL

Base Paper Abstract:

Approximate computing is a promising approach for reducing power consumption and design complexity in applications that accuracy is not a crucial factor. Approximate multipliers are commonly used in error-tolerant applications. This paper presents three approximate 4:2 compressors and two approximate multiplier designs, aiming at reducing the area and power consumption, while maintaining acceptable accuracy. The paper seeks to develop approximate compressors that align positive and negative approximations for input patterns that have the same probability. Additionally, the proposed compressors are utilized to construct approximate multipliers for different columns of partial products based on the input probabilities of the two compressors in adjacent columns. The proposed approximate multipliers are synthesized using the 28nm technology. Compared to the exact multiplier, the first proposed multiplier improves power × delay and area × power by 91% and 86%, respectively, while the second proposed multiplier improves the two parameters by 90% and 84%, respectively. The performance of the proposed approximate methods was assessed and compared with the existing methods for image multiplication, sharpening, smoothing and edge detection. Also, the performance of the proposed multipliers in the hardware implementation of the neural network was investigated, and the simulation results indicate that the proposed multipliers have appropriate accuracy in these applications.

List of the following materials will be included with the Downloaded Backup:

Proposed Title :

Improvement of this project :

Software Implementation:

Proposed System:

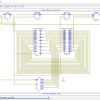

Electroencephalogram (EEG) is a form of cardiovascular measurement and dynamic information from the Brain conditions. However, numerous noises usually harm the amplitude and time period of the signal from the EEG signal, at following a transition of the analog EEG signal from the sensor module into a digital format. The appropriate digital filter may be used to remove different forms of noise such as Baseline Wander, Power line interference, High frequency noise and Physiological Artifacts. The Digital FIR filter will have prospected to reduce the artifacts in the EEG signals. This Digital FIR filter can have more performance by using 8 TAP numbers such as multiplying, delaying and getting more effectiveness. This proposed work would implement a 1 norm minimization in the FIR filter with liner step method to minimize sparse complexity and reduce the mini-max approximation error for sparse maximization. This proposed work of Digital FIR filter, which developed using two different Approximate computing multiplier to reducing power consumption and design complexity. Given these facts, several rules for selecting indicators of potential zero coefficients to be used in 1 standard optimization are adopted in the proposed algorithm. The efficacy of the proposed design algorithm was developed in Verilog HDL, simulated and synthesized in Vivado Zynq FPGA, and finally prove all the parameters in terms of area, delay and power.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

HDFC BANK ACCOUNT:

₹25,000.00 Original price was: ₹25,000.00.₹8,000.00Current price is: ₹8,000.00.

₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

Copyright © 2026 Nxfee Innovation.